# Towards quantum transport in single-crystalline PbTe nanowire MOSFET devices

M.J.G. Kamphuis, BSc.

February 5<sup>th</sup>, 2021

Supervisors: Prof. dr. E.P.A.M. Bakkers, A.G. Schellingerhout (MSc) Eindhoven University of Technology - Department of Applied Physics Advanced Nanomaterials and Devices group

Prof. dr. D.A.M. Vanmaekelbergh, Dr. I. Swart Utrecht University - Debye Institute for Nanoscience Condensed Matter and Interfaces group

Final version

For my grandparents

# Table of natural constants

| Planck constant             | h            | $6.6261 \cdot 10^{-34}$ | Js  |

|-----------------------------|--------------|-------------------------|-----|

| Planck's constant (reduced) | $\hbar$      | $1.0546 \cdot 10^{-34}$ | Js  |

| Boltzmann constant          | $k_b$        | $1.3806 \cdot 10^{-23}$ | J/K |

| Vacuum permittivity         | $\epsilon_0$ | $8.8542 \cdot 10^{-34}$ | F/m |

| Vacuum permeability         | $\mu_0$      | $1.2566 \cdot 10^{-6}$  | H/m |

| Elementary charge           | e            | $1.6022 \cdot 10^{-19}$ | C   |

| Electron mass               | $m_0$        | $9.1093 \cdot 10^{-31}$ | kg  |

| Bohr magneton               | $\mu_B$      | $9.2740 \cdot 10^{-31}$ | J/T |

# Abstract

PbTe is a narrow band gap semiconductor with a remarkably high Landé g-factor and spin-orbit interaction. This makes it a very interesting possible candidate for Majorana devices. Therefore the MBE growth of low-defect single-crystalline PbTe nanowires has been developed. This research aimed to develop a fabrication recipe for reliable fabrication of nanowire MOSFET devices. And to use these to characterise the electronic transport properties of these nanowires.

However, Schottky barriers were formed between the nanowire and the Ti/Au source and drain contacts, partially due both the material choice and the fabrication procedure.

The Schottky barriers have been characterised based by fitting the measured transport data with a thermionic emission model. This established thermionic emission as the dominant transport mechanism, and allowed for the determination of the Schottky barrier height ( $\Phi_B^{\text{eff}} = 0.55 \pm 0.25$ V).

Despite the Schottky barriers, an attempt has been made to extract the carrier mobility and density from the transport data. Carrier densities in the order of  $\sim 10^{18}$  cm<sup>-3</sup> have been obtained. This seems a plausible value compared to the carrier densities of other narrow band gap semiconductors (InAs, InSb). The obtained mobilities ( $\mu_e = 0.02 - 0.12$  cm<sup>2</sup>/Vs) are two orders of magnitude lower than in other semiconductors. However, it was to be expected that the mobility of the device was heavily impacted by the presence of barriers at the contact interface.

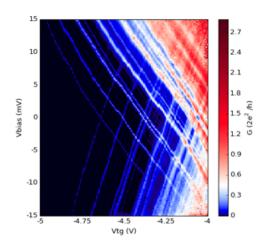

PbTe nanowires grown in Eindhoven have been fabricated into similar devices in the Frolov group at the University of Pittsburgh. There cryogenic transport measurements were performed on the devices. The barriers at the metal/semiconductor interface, though much less pronounced, turned the nanowires into nanowire quantum dots. Some curious signatures were observed in the transport characteristics of these dots. Some of these features can be explained to be signatures of Wigner localisation of electrons in the dot. Steps have been made in the full quantum-mechanical modelling of this system, but still a lot of time has to be invested to completely reproduce the experimental results.

# TABLE OF CONTENTS

| Intro   | oductio        | n                                            | 3      |

|---------|----------------|----------------------------------------------|--------|

| I       |                | ent Majorana quasiparticles                  | 3      |

| -       | I-A            | Dirac and Majorana: the foundation .         | 3      |

|         | I-B            | The Kitaev chain                             | 4      |

|         | I-C            | Physical realisation: semiconductor-         | т      |

|         | гc             | •                                            | 4      |

|         | ID             | superconductor heterostructures              |        |

|         | I-D            | Majorana's for quantum comupting             | 6      |

| Π       |                | ersus the status quo                         | 6      |

|         | II-A           | Experimental signatures of Majorana          | -      |

|         |                | fermions                                     | 6      |

|         | II-B           | PbTe vs InAs and InSb                        | 6      |

| III     | Structu        | re of this thesis                            | 7      |

| рьти    | e nanov        | wing                                         | 8      |

| -       |                |                                              |        |

| I<br>TT |                | Material properties                          | 8<br>9 |

| II      | Nanow          | ire growth                                   | 9      |

| Nand    | owire N        | MOSFET devices                               | 11     |

| I       |                | nic properties of semiconducting mate-       |        |

| rials   | Litter         | the properties of semiconducting mate        | 11     |

| I Iulis | I-A            | Carrier densities                            | 11     |

|         | I-B            | Electronic transport                         | 12     |

| п       |                | semiconductor interfaces                     | 12     |

| 11      | II-A           |                                              | 12     |

|         |                | The Schottky-Mott model                      |        |

|         | II-B           | Mechanisms of electronic transport           | 13     |

|         | II-C           | Surface states and Fermi level pinning       | 15     |

| III     |                | ng principles of the nanowire MOSFET         | 16     |

|         | III-A          | MOS stack: gate behaviour                    | 17     |

|         | III-B          | Ideal nanowire MOSFET operation              |        |

|         |                | and extraction of transport properties .     | 19     |

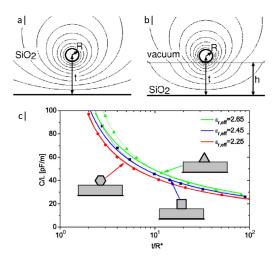

|         | III-C          | Capacitance                                  | 20     |

| Devi    | ce fahr        | rication                                     | 22     |

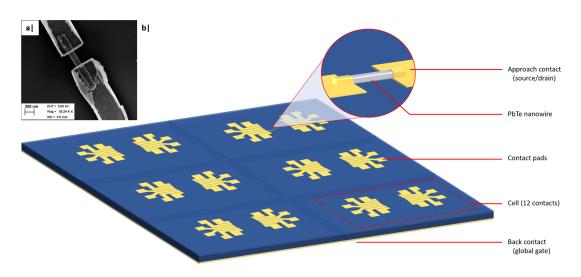

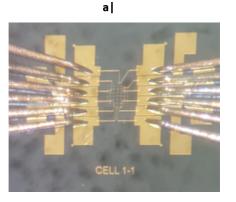

| I       |                | architecture                                 | 22     |

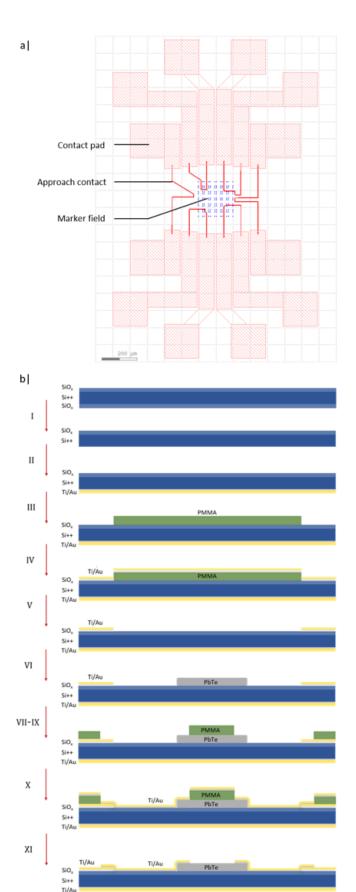

| -       |                | ation recipe                                 | 22     |

| 11      | raunca         | ation recipe                                 | 23     |

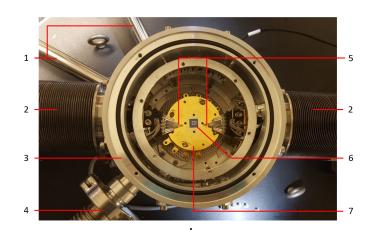

| Elect   | tronic 1       | transport measurements                       | 25     |

|         |                | -                                            |        |

| Expe    |                | tal results                                  | 27     |

| Ι       |                | contacts on PbTe nanowires                   | 27     |

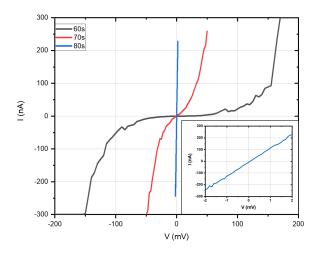

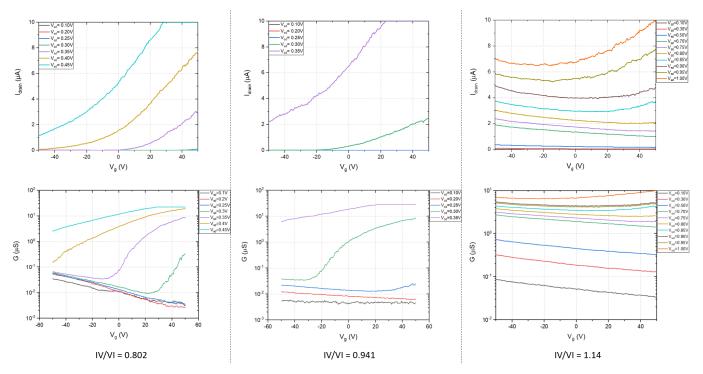

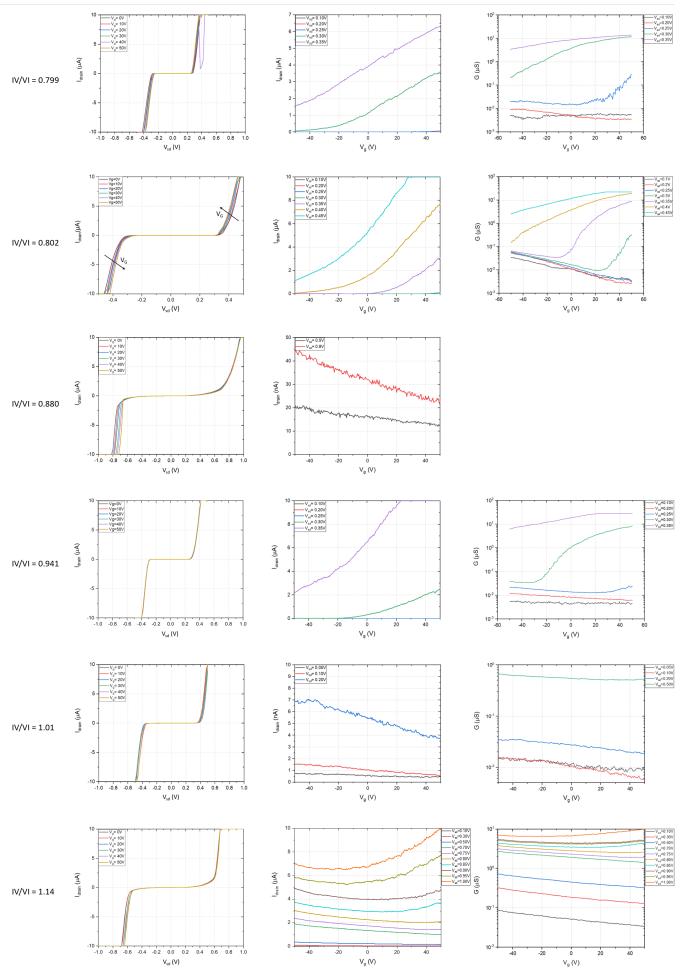

|         | I-A            | Introduction to the samples: a growth series | 28     |

|         | I-B            | Schottky barrier characterisation            | 28     |

|         | I-C            | Gate voltage dependence                      | 31     |

|         | -              | • •                                          |        |

| п       | I-D<br>Transco | Temperature dependence                       | 31     |

| II      |                | onductance and transport properties          | 31     |

|         | II-A           | Doping character                             | 33     |

|         | II-B           | Transport properties                         | 34     |

| Tran    | isport f       | through nanowire quantum dots                | 35     |

| I       |                | nic transport measurements on PbTe           | 55     |

| nanov   |                | ine transport incasurements on FDIe          | 35     |

| nanov   | w 11 CS        |                                              | 55     |

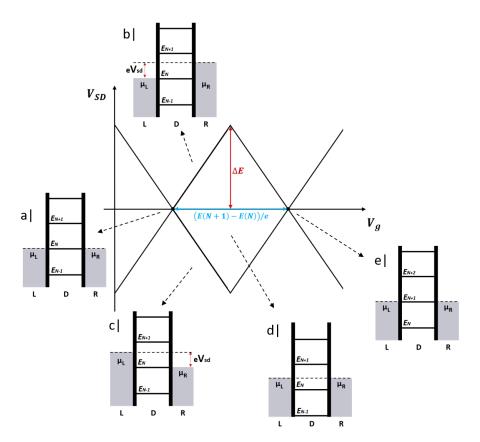

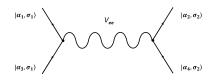

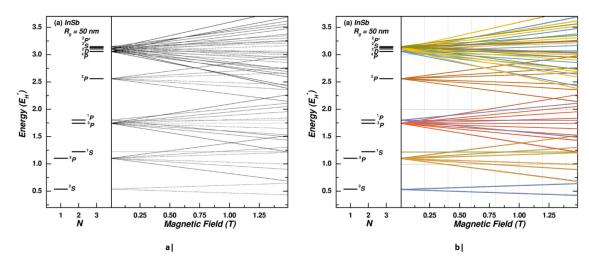

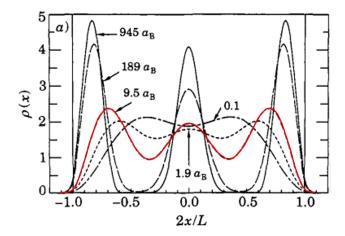

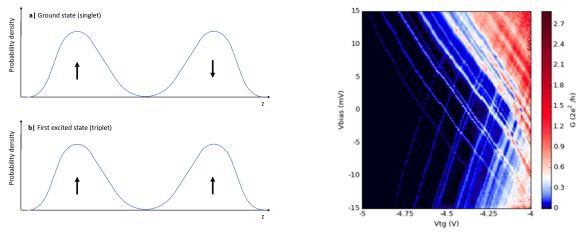

| II<br>III | II-A<br>II-B<br>II-C | Interaction modelThe quantum dot HamiltonianMany particle eigenstatesTransition rates: transport equationsspectra of quantum dots | 37<br>37<br>37<br>38<br>38 |

|-----------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| _         | U                    | remarks                                                                                                                           | 41                         |

| I<br>T    |                      | tion of PbTe devices                                                                                                              | 41                         |

| II        | Improv               | ements for measurements and data anl-                                                                                             |                            |

| ysis      | C                    |                                                                                                                                   | 42                         |

| III       | Conngu               | iration interaction model                                                                                                         | 43                         |

| Арр       | endices              |                                                                                                                                   | 44                         |

| I         |                      | fabrication recipe                                                                                                                | 44                         |

|           | I-A                  | Back gate contact                                                                                                                 | 44                         |

|           | I-B                  | Contact pads and markers                                                                                                          | 44                         |

|           | I-C                  | Nanowire transfer                                                                                                                 | 44                         |

|           | I-D                  | Approach contacts                                                                                                                 | 44                         |

| Π         | Data fit             | ting                                                                                                                              | 46                         |

| III       | Suppler              | nentary data                                                                                                                      | 46                         |

| Ш    | Supplementary data |

|------|--------------------|

| Refe | rences             |

# Introduction

Quantum computing is a branch of quantum physics that currently enjoys a lot of scientific and commercial interest. Once physically realised, a quantum computer will be able to harness fundamental properties of quantum mechanics, such as linear superposition and entanglement of quantum states, that are not available to classical computers.

Algorithms that manage to fully utilise these properties could revolutionise our current way of processing and encrypting data. These could significantly speed up certain computations. For example, Shor's prime number factor factorisation algorithm would be exponentially faster than a classical analogue [1]. This would essentially break our current way of encrypting data. Another application of quantum mechanics is the simulation of systems that themselves are quantum mechanical in nature. Think for example of the development of new medicines, or solving high-temperature superconductivity. The calculation power (or number of bits) that a classical computer would require for the simulation of such a system scales exponentially with the number of degrees of freedom, due to its probabilistic nature. This makes the simulation of larger quantum mechanical models fundamentally impossible using a classical computer. However, Feynman already showed in 1982 that certain many-body quantum Hamiltonians can be simulated exponentially faster on a quantum computer than on a classical computer [2], because the calculations themselves are probabilistic in nature.

However, quantum computers have some issues of their own. The most important is quantum decoherence: the state of a system will only remain in a coherent superposition of states for a finite time. Interactions with the environment may collapse the wave function of a quantum state, thereby destroying the information encrypted in it.

Topological quantum computing proposes to exploit the emergent quasiparticles in many-particle systems to encode and manipulate quantum information. These emergent states are fundamentally non-local in nature, and are therefore immune to the usual (localised) sources of quantum decoherence. This makes topological quantum computing intrinsically fault-tolerant. One theorised realisation of a topological quantum computer is based on Majorana quasiparticles in one-dimensional hybrid semiconductor superconductor systems, see section I-C.

A recently proposed material system that could host these Majorana quasiparticles consists of a lead telluride (PbTe) nanowire with lead (Pb) as a superconductor. This thesis focuses on the electronic characterisation of the semiconductor part of this material system, and explores fundamental challenges in device design and fabrication.

#### I. EMERGENT MAJORANA QUASIPARTICLES

First a concise, but complete overview of the relevant Majorana physics will be presented. This should also clarify the requirements for a material system to host Majoranas.

# A. Dirac and Majorana: the foundation

In 1928, Paul Dirac's efforts to unify special relativity and quantum mechanics resulted in the now well-known Dirac equation (eq.1), which is the relativistic wave equation for massive spin- $\frac{1}{2}$  fermions:

$$(i\hbar\gamma^{\mu}\partial_{\mu} - mc)\psi = 0, \qquad (1)$$

with *m* the particle mass, and  $\psi$  the Dirac spinor fields. Special relativity creeps into this equation through the requirement that the  $\gamma^{\mu}$ -matrices<sup>1</sup> are 4×4 matrices that generate the Clifford algebra [3]:

$$\{\gamma^{\mu}, \gamma^{\nu}\} = 2\eta^{\mu\nu},\tag{2}$$

with  $\eta^{\mu\nu}$  the Minkowski metric tensor. This equation yielded a remarkable prediction: the existence of antimatter. The existence of the antiparticle to the electron, the so-called positron, was indeed confirmed only a year later [4]. Antiparticles have the same mass and spin as their "regular" counterparts, but carry a charge of the opposite sign. This implies that neutral particles can be identical to their antiparticles. More formally, this requires that the particle field is equal to its Hermitian conjugate:  $\psi = \psi^{\dagger}$ . This can only be true if it is a completely real-valued field.

In 1937, Italian physicist Ettore Majorana had the insight that the solutions to the Dirac equations become real, if the  $\gamma^{\mu}$ -matrices were chosen to be completely imaginary [5]. This can be achieved by defining four alternative  $\tilde{\gamma}^{\mu}$ -matrices that satisfy the same anticommutation relations (eq.2) as Kronecker products of the Pauli matrices [3]:

$$\begin{split} \tilde{\gamma}^{0} &= \sigma_{2} \otimes \sigma_{1} \\ \tilde{\gamma}^{1} &= i\sigma_{1} \otimes \mathbb{1}_{2} \\ \tilde{\gamma}^{2} &= i\sigma_{3} \otimes \mathbb{1}_{2} \\ \tilde{\gamma}^{3} &= i\sigma_{2} \otimes \sigma_{2} \end{split}$$

(3)

With these new  $\tilde{\gamma}^{\mu}$ -matrices the Dirac equation (eq.1) can be rewritten as the Majorana equation for real fields  $\phi$ :

$$(i\hbar\tilde{\gamma}^{\mu}\partial_{\mu} - mc)\phi = 0, \qquad (4)$$

<sup>&</sup>lt;sup>1</sup> Conventional choice for the matrices  $\gamma^{\mu}$ , with  $\sigma_i$  Pauli matrices, and  $\mathbb{1}_2$  the 2×2 identity matrices.

In his honour, particles that satisfy this equation are now known as Majorana fermions (MFs).

These Majorana fermions turn out to be rather elusive, as to date no irrefutable evidence for their existence has been found. In the twentieth century, the concept of Majorana fermions was mostly related to high-energy physics. For example, neutrinos have been speculated to be particles of this kind. However, this has been proven very difficult to verify: neutrinos are extraordinarily weakly interacting particles, making them difficult to detect [3][4].

#### B. The Kitaev chain

More recently it has been recognised that certain condensed matter systems may also support Majorana fermions as emergent quasiparticles. A toy model that manifests these emergent Majorana fermions, is the Kitaev chain [6].

Consider a chain of N fermions with a spin alignment along the z-axis, and only nearest neighbour interactions. Assuming a ferromagnetic coupling, the ground state of such a system will consists of particles with aligned spins (e.g.:  $|\uparrow\uparrow\uparrow\uparrow\uparrow\uparrow\dots\rangle$ ). An excitation of this system will consist of a single flipped spin (e.g.:  $|\uparrow\uparrow\downarrow\uparrow\uparrow\uparrow\dots\rangle$ ). In second quantisation notation this can be expressed in terms of fermionic creation  $c_i^{\dagger}$  and annihilation  $c_i$  operators for an excitation/spin flip at position *i*:

Ground state =

$$|\uparrow\uparrow\uparrow\uparrow\uparrow ...\rangle = |0\rangle$$

First excitation =  $|\uparrow\uparrow\downarrow\uparrow\uparrow ...\rangle = c_i^{\dagger}|0\rangle$

(5)

In this description the spin degree of freedom is entirely redundant, as the nature of the excitation created by  $c_i^{\dagger}$  is not specified in this notation. Therefore this model is known as the spinless fermion chain.

Now we recall that the solutions to the Majorana equation are real fields. In the second quantisation formalism this criterion translates to real-valued Majorana creation and annihilation operators:  $\gamma_i = \gamma_i^{\dagger}$ , with  $\{\gamma_i, \gamma_j\} = 2\delta_{ij}$ . From these requirements it can easily be confirmed that the creation and annihilation operators for (conventional) Dirac fermions can be defined in terms of the Majorana operators:

$$c_{i} = \frac{1}{2}(\gamma_{i,1} + i\gamma_{i,2}) c_{i}^{\dagger} = \frac{1}{2}(\gamma_{i,1} - i\gamma_{i,2})$$

(6)

In other words: one conventional fermion can be expressed as a combination of two Majorana fermions.

Kitaev suggested that in a fermionic chain, new fermions  $\tilde{c}_i$  can be redefined by combining Majorana operators from adjacent sites:

$$\tilde{c}_{i} = \frac{1}{2} (\gamma_{i,2} + i\gamma_{i+1,1})$$

$$\tilde{c}_{i}^{\dagger} = \frac{1}{2} (\gamma_{i,2} - i\gamma_{i+1,1})$$

(7)

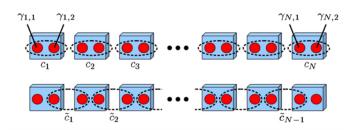

This reordering is schematically shown in fig. 1.

Fig. 1: Schematic depiction of the reordering of the fermionic chain as proposed by Kitaev. The top panel shows a chain of N conventional fermions  $c_i$  (blue), and its component Majorana fermions  $\gamma_{i,1}$  and  $\gamma_{i,2}$  (red). The bottom panel shows the reordering of adjacent MFs into a chain of N-1 fermions  $\tilde{c}_i$  (dotted ellipses) and the two edge MFs. Reprinted from Leijnse and Flensberg [7].

Now a Hamiltonian for this fermionic chain that only considers nearest neighbour interactions can be defined:

$$\mathcal{H}^{\text{Kitaev}} = -\mu \sum_{i=1}^{N} c_i^{\dagger} c_i - \sum_{i=1}^{N-1} \left( t c_i^{\dagger} c_{i+1} + \Delta c_i c_{i+1} + \text{h.c.} \right), \quad (8)$$

with  $\mu$  the chemical potential, and t the tight-binding interaction strength between neighbouring sites. Notice that the coupling constant  $\Delta$  between two particles with aligned spins is identified as the superconducting gap. This implies that this Hamiltonian requires triplet Cooper pairing, or pwave superconductivity.

Consider now the special case  $\mu = 0$  and  $t = \Delta$ . Then the Kitaev Hamiltonian (eq.8) can be rewritten in terms of reordered fermionic operators (eq.7): [7]:

$$\mathcal{H}^{Kitaev} = 2t \sum_{i=1}^{N-1} \tilde{c}_i^{\dagger} \tilde{c}_i \tag{9}$$

This is just a formal way of reordering the Hamiltonian: it is expressed in a different basis of eigenstates. Notice that this Hamiltonian only counts N - 1 fermionic states: the two Majorana operators at the ends of the wire ( $\gamma_{1,1}$  and  $\gamma_{N,2}$ ) are completely missing. Together these form a highly non-local state: the Majorana zero-mode (MZM):

$$\tilde{c}_M = \frac{1}{2}(\gamma_{1,1} + i\gamma_{N,2}) \tag{10}$$

Because this Majorana zero-mode is not included in the Hamiltonian, it does not cost any energy to occupy this state (hence the name zero-mode). As a result, all the energy states of the Kitaev chain become two-fold degenerate. As will be discussed in sectionI-D, this is essential for the application of MZMs as qubits.

Up until now only the case  $\mu = 0$  and  $t = \Delta$  was considered, but it can be show that the Majorana edge states remain as long as the chemical potential resides within the gap  $|\mu| < 2t$ [6].

# *C. Physical realisation: semiconductor-superconductor heterostructures*

As noted before, the Kitaev model requires p-wave superconductivity to host Majorana edge states. Unfortunately, p-wave superconductors do not exist in nature. However, if a material system can be engineered whose Hamiltonian closely resembles a pwave superconductor, it may still be able to host a MZM. In this context, "close enough" means in this context that the Hamiltonian of the material system can be continuously transformed into the Hamiltonian of a p-wave superconductor, without ever closing the superconducting gap [7].

Lutchyn et al.[8] and Oreg et al.[9] proposed that onedimensional semiconductor-superconductor heterostructures could indeed host MZMs.

Let's start by considering a long and thin nanowire. Electrons in such a nanowire will be strongly confined in the transverse direction when the wire cross-section is small compared to the electron Fermi wavelength. This confinement results in well-separated subbands. Using (local) gates on the wire, conductance channels in the wire can be opened or closed for electronic transport. If only one channel is opened, the wire can effectively be considered as a 1D system [7].

Generally the Hamiltonian of a semiconductor in terms of the fermionic fields  $\Psi_{\sigma}$ **r**:

$$\mathcal{H}_{0} = \sum_{\sigma=\uparrow,\downarrow} \int d\mathbf{r} \Psi_{\sigma}^{\dagger}(\mathbf{r}) H_{0}(\mathbf{r}) \Psi_{\sigma}^{\dagger}(\mathbf{r}) , \qquad (11)$$

where the single-particle Hamiltonian  $H_0(\mathbf{r})$  is given by:

$$H_0(\mathbf{r}) = \frac{\mathbf{p}^2}{2m^*} - \mu + \alpha(\mathbf{E}(\mathbf{r}) \times \mathbf{p}) \cdot \bar{\sigma} + \frac{1}{2}g\mu_B \mathbf{B}(\mathbf{r}) \cdot \bar{\sigma} \quad (12)$$

Here  $m^*$  is the effective electron mass in the semiconductor, and  $\bar{\sigma}$  is a vector of Pauli matrices. The second to last term describes a generic spin-orbit coupling of strength  $\alpha$ . **E** is the electric field experienced by the electrons. The last term includes Zeeman splitting in the model. **B** is an applied field and g is the Landé g-factor.

Superconductivity can be proximity-induced in a nanowire, if a defect-free interface with a superconductor is formed. In this case electrons can tunnel between the two materials. Therefore an electron-electron pairing term with coupling strength  $\Delta(\mathbf{r}, \mathbf{r}')$  can be added to this Hamiltonian. The strength of this term depends on both materials, as well as the quality of the interface.

Because of electron-hole symmetry it is conventional to define the Nambu spinors when describing superconducting systems<sup>2</sup>:

$$\bar{\Psi}(\mathbf{r}) = \begin{pmatrix} \Psi_{\uparrow}(\mathbf{r}) \\ \Psi_{\downarrow}(\mathbf{r}) \\ \Psi_{\downarrow}^{\dagger}(\mathbf{r}) \\ -\Psi_{\uparrow}^{\dagger}(\mathbf{r}) \end{pmatrix}$$

(13)

Now the eigenspinors of the Bogoliubov-de Gennes (BdG) equation describes quasiparticle excitations in the proximitised system <sup>3</sup>:

$$\bar{H}_0(\mathbf{r})\bar{\Psi}_i(\mathbf{r}) + \int d\mathbf{r}'\bar{\Delta}(\mathbf{r},\mathbf{r}')\bar{\Psi}_i(\mathbf{r}') = E_i\bar{\psi}_i(\mathbf{r}) \qquad (14)$$

$^2$  Eq.6 (or eq.7) can be rewritten as:

$$\gamma_{i,1} = c_i^{\dagger} + c_i, \qquad \gamma_{i,2} = i(c_i^{\dagger} - c_i)$$

From writing the operator expressions in this form, it is apparent that the Majorana operators can be expressed as a superposition of an electron and a hole, reminiscent of a Bogoliubov quasiparticle in a superconductor [7][10].

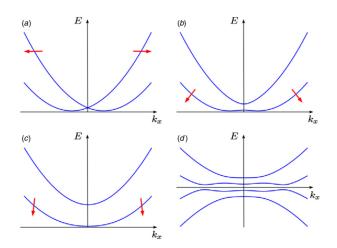

Fig. 2: One-dimensional dispersion relation of a nanowire: a| with Rashba spin-orbit coupling. This shifts the spin-degenerate subbands along the momentum axis in opposite directions.

b| with an additional (small) magnetic field. The resulting Zeeman splitting lifts the spin-degeneracy and opens the gap at  $k_x = 0$ . c| with SOI and a larger magnetic field, which increases the gap and the

spin alignment in the subbands.

d with SOI, an external magnetic field, and proximity-induced superconductivity: these are the dispersion curves are the solution to the Bogoliubovde Gennes equation. Both the electron and hole bands are plotted here. Reprinted from Leijnse and Flensberg [7]

Because the Majorana quasiparticles are their own antiparticles  $(\bar{\Psi}_i^{\dagger}(\mathbf{r}) = \bar{\Psi}_i(\mathbf{r}))$ , they can only ever be eigenstates of the BdG-equation at E = 0. So in correspondence with the Kitaev model, this physical system can indeed host Majorana zero modes.

Let's now examine the dispersion of electrons in a semiconductor nanowire (fig.2) for a bit more insight of the role of the different components in this Hamiltonian.

In its simplest form, this dispersion takes on the form of a one-dimensional parabola, due to the strong confinement of the electron wavefunctions in the transverse directions. Spin-orbit interaction (SOI) lifts the spin-degeneracy: the two spin-subbands shift in opposite directions along the  $k_x$ -axis (see fig.2a) [11].

The addition of a magnetic field perpendicular to the nanowire axis results in Zeeman splitting of the energy bands (see fig.2b). This opens a gap at  $k_x = 0$ . If the chemical potential is tuned inside the gap, only the bottom band is occupied. This essentially transforms the system to a continuous version of Kitaev's spinless fermion chain [12]. The stronger the applied magnetic field, the wider the area in momentum space that is effectively spinless.

Proximity-induced superconductivity pairs electrons with opposite spin in Cooper pairs. This pairing competes with the Zeeman splitting of the energy bands for the alignment

<sup>3</sup> Here  $\bar{H}_0(\mathbf{r})$  and  $\bar{\Delta}(\mathbf{r}, \mathbf{r}')$  are the 4×4 extensions of the 2×2 singleparticle Hamiltonian and pairing potential matrices, respectively:

$$\bar{H}_0(\mathbf{r}) = \begin{pmatrix} H_0(\mathbf{r}) & \hat{0} \\ \hat{0} & -\sigma_y H_0^*(\mathbf{r}) \sigma_y \end{pmatrix}, \qquad \bar{\Delta}(\mathbf{r}, \mathbf{r'}) = \begin{pmatrix} \hat{0} & \Delta(\mathbf{r}, \mathbf{r'}) \hat{1} \\ \Delta(\mathbf{r}, \mathbf{r'}) \hat{1} & \hat{0} \end{pmatrix}$$

of the spins in the nanowire [12][13].

For weak magnetic fields the superconducting pairing will dominate; the nanowire will behave as a trivial s-wave superconductor. This dispersion will still display a gap, but this is merely the conventional superconducting gap. If the Zeeman splitting dominates, a topological phase transition takes place (the bands invert), and the topological gap opens up. Electrons are now still paired, but with aligned spins: the system is in a p-wave superconducting state. So the nanowire is in the topological state if:

$$\frac{1}{2}g\mu_B B \geqslant \sqrt{\mu^2 + \Delta^2} \,. \tag{15}$$

When only a part of the nanowire is proximitised by a superconductor, also only the covered part can be in the topological state. Because the bands are inverted in the topological state, there has to be a point where the bands cross when moving from the trivial to the superconducting regions in the wire. Because electron-hole symmetry in superconductors, this crossing has to occur exactly at zero energy. This is where the Majorana zero mode can occur: at the interface between the trivial and superconducting regions. Therefore it is also known as a Majorana edge mode.

From this discussion a short list with requirements for a device that can host MZMs can be made:

- 1) A low-defect 1D (nanowire) semiconductor material

- 2) Strong Rashba spin-orbit interaction

- 3) Large Landé g-factor

- 4) Proximity-induced superconductivity

- 5) Global and local gates to tune the chemical potential into the topological gap.

This list will be used for further discussions of suitable material combinations and device designs.

For a more formal description of discussion above, the review papers by Leijnse and Flensberg [7], Alicea [14], and Aguado [15] are highly recommended.

# D. Majorana's for quantum comupting

The fundamental building block of a quantum computer is the quantum bit (qubit). It has been proposed that socalled Majorana qubits can be created based on these Majorana zero-modes. Operations can be performed on such a qubit based on its exchange statistics. When two bosons (fermions) exchange positions, the total system acquires a phase factor of +1 (-1). However, MZMs are non-Abelian anyons [16]. This means that the phase factor the system acquires upon the exchange of two MZMs depends on the path taken. Moreover, if multiple operations are performed in succession, the accumulated phase factor also depends on the order of the operations. Therefore information can be encoded in the phase of the Majorana qubits, by exchanging the positions of the MZMs [17][18]. This process is called braiding.

Because the MZMs are highly non-localised emergent quasiparticles, the Majorana qubits based on them are very robust to local perturbations: they are topologically protected [19]. Therefore computation operations are inherently fault tolerant.

## II. PBTE VERSUS THE STATUS QUO

Here a short overview of the state-of-the-art experiments and material systems used for the detection of MZMs will be given. This will be compared to the PbTe/Pb material system. From this comparison the motivation for this project should become clear.

## A. Experimental signatures of Majorana fermions

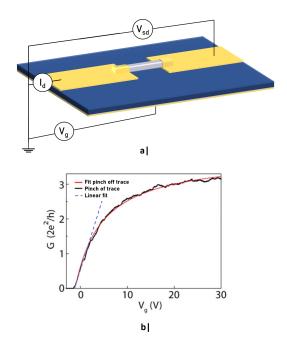

Since the theoretical prediction in 2001 by Kitaev [6], significant steps have been undertaken to experimentally verify the existence of MZMs in condensed matter systems. The first signature, the zero-bias conductance peak, was reported by Mourik et al. in 2012 [13]. However, to date no conclusive evidence for their existence has been presented.

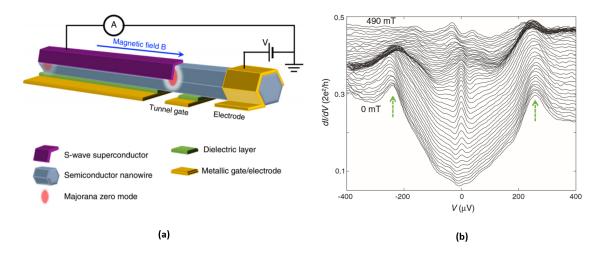

The detection scheme used by Mourik et al. and numerous experiments since then [20][?][21], is based on tunneling spectroscopy (see fig.3). In these devices a nanowire is placed on a substrate with back gates. These gates can be used to tune the Fermi level in the wire into the topological gap. Two contacts are deposited onto the wire: a superconducting contact, and a conventional Ohmic contact. A separate back gate can be found underneath the part of the wire that is covered by neither of the contacts. If a negative voltage is applied to that gate, a tunnel barrier for electrons is formed between the topological region and the Ohmic comtact.

When a magnetic field is applied, Majorana zero modes are formed at the edges of the topological region (indicated in pink in fig.3a). If a bias voltage is applied between the two contacts, tunneling through the barrier can occur. This is shown as a waterfall plot in fig.3b for various magnetic field strengths. Here the emergence of the Majorana zero mode (MZM) as a function of the applied Zeeman field can be seen as a zero-bias conductance peak. For low fields the topological gap is closed, and thus no MZM is permitted. If the applied field is high enough to open the gap, the in-gap states clearly emerge at zero bias, giving rise to a conductance peak.

However, all signatures of Majorana fermions measured to date are no definitive proof for their existence. For example, in the case of the experiment by Mourik et al. the zero-bias peaks do not have the predicted amplitude of one conductance quantum:  $G_0 = \frac{2e^2}{h}$ . Several other phenomena have been proposed that can show similar signatures: Andreev bound states, weak antilocalisation, and the Kondo effect [20][21]. Braiding experiments can reveal the non-Abelian properties of the Majorana fermions, and thus ultimately proof their existence [17][22].

# B. PbTe vs InAs and InSb

Several material systems have been proposed as physical realisations of the semiconductor-superconductor heterostructure discussed in sec.I-C. Most notably indium arsenide (InAs) or indium antimonide (InSb) nanowires with aluminium as a superconductor. Both semiconductor materials have a large Landé g-factor, which requires lower

Fig. 3: (a) Schematic depiction of the device used to detect the Majorana zero modes. A nanowire is contacted with a normal and a superconducting contact, over which a voltage is applied and the resulting current measured. A global gate underneath the superconducting region can be used to tune the Fermi level to be in the topological gap. The local tunnel gate can be used to either tune the number of open conduction channels in the wire, or form a tunnel barrier. Reprinted from Zhang et al. [21].

(b) Waterfall plot of the measured conductance (dI/dV) as a function of the applied bias voltage and the applied magnetic field. It can clearly be seen that zero-bias peaks get formed when the applied magnetic (Zeeman) field is high enough to open the topological gap. Reprinted from Mourik et al. [13].

magnetic fields to open the gap. This is important because the magnitude of the applied magnetic field is limited by the critical field of the superconductor. Both materials also have a large spin-orbit strength, which leads to more pronounced subband splitting.

However, the previous section ended with a short discussion on why the existence MZMs of has not yet irrefutably been proven. Most of the state-of-the-art experiments up until now have been performed with either InAs or InSb nanowires. Therefore another material system has been proposed: lead telluride nanowires with superconducting lead. A comparison between the three semiconducting materials is shown in the table below:

| Material                                       | InAs             |      | InSb               |      | PbTe |      |

|------------------------------------------------|------------------|------|--------------------|------|------|------|

| Bandgap (eV at 300K)                           | 0.35             | [23] | 0.18               | [23] | 0.31 | [23] |

| Landé g-factor                                 | 20-50            | [24] | 58-64              | [25] | 66   | [26] |

| Spin-orbit energy (µeV)                        | 10               | [24] | 230                | [27] | 330  | [28] |

| Electron mobility (cm <sup>2</sup> /Vsat 4.2K) | $3.3 \cdot 10^4$ | [29] | $7.7 \cdot 10^{4}$ | [30] | -    |      |

PbTe is predicted to have an even higher g-factor than both InAs and InSb. Moreover, experiments on PbTe wires used for this project have already shown that the spin-orbit interaction in these wires is stronger than in the InAs or InSb nanowires used in the leading experiments performed in the last decade [28].

Another big advantage of PbTe over the other two materials is the pairing with the superconductor. Diffusion of aluminium atoms into the InAs or InSb nanowire reduces the quality of the interface between the superconductor and the nanowire. Lead can be grown approximately lattice matched with the PbTe nanowire [26], and diffusion of lead into PbTe does not pose an issue. Therefore this material system is more likely to produce a clean interface, and therefore a hard superconducting gap.

# III. STRUCTURE OF THIS THESIS

This work focuses on the characterisation of the (quantum) transport properties of MBE grown PbTe nanowires, and works towards their application in Majorana devices. Therefore three main goals are set:

- Develop devices that allow transport measurements to be performed on the PbTe nanowires.

- Characterisation material properties (carrier mobility and density, band gap, g-factor) and compare to InAs and InSb.

- Achieve reliable tunability of the carrier concentration by controlling the IV/VI ratio during growth.

Chapter 2 elaborates on the material properties of PbTe, and on the nanowire growth. This will be followed by a discussion on transport phenomena in semiconductor materials and the working principles of MOSFET devices in chapter 3. Next, chapters 4 and 5 explain the practical matters of the device fabrication and measurement procedures. After which the results of this project are discussed in chapter 6.

During this project, quantum transport measurements were done in Sergey Frolov's group at the University of Pittsburgh on similar devices with the same PbTe wires from Eindhoven as were used in this project. There some interesting and unexpected results were found: a quantum dot was formed in the wire, and it was found that spin blockade was a stronger effect than Coulomb blockade in transport measurements. Chapter 7 explains a (partially finished) fully quantum mechanical model to explain these results.

Finally, chapter 8 will present some concluding remarks, and some follow-up experiments will be proposed.

# PbTe nanowires

Lead telluride (PbTe) is a group IV/VI semiconductor material. Even though PbTe/Pb has only recently been proposed as a suitable material system for Majorana devices, PbTe has been extensively studied for other applications. Due to its small direct bandgap, a lot effort has been put into the study of its optical properties for photodetectors [31][32][33]. The thermodynamic properties of PbTe have also been studied elaborately for application in thermoelectric devices [34].

This chapter will go over the relevant material properties for our purposes (section I), and then briefly go over the nanowire growth (section II).

# I. PBTE: MATERIAL PROPERTIES

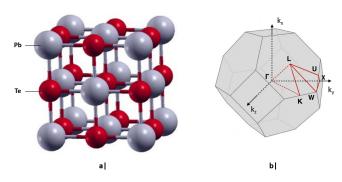

Like most lead chalcogenides, PbTe crystallises in the rock salt crystal structure [23]; this is shown schematically in fig.4a. This crystal structure can also be viewed as two interpenetrating FCC sublattices: one sublattice for each element. The bonds between the atoms have a mixed covalent-ionic character, with an ionicity  $f_i = 0.65$  [35][36].

Fig. 4: Sketches of  $\mathbf{a}|$  the crystal structure (adapted from [37]), and  $\mathbf{b}|$  the first Brillouin zone (reprinted from [38]) of PbTe.

The first Brillouin zone is depicted in fig.4b. The most important symmetry points in reciprocal space have been indicated. PbTe has a narrow direct bandgap at the L-point, as can be seen in fig.5. At room temperature (300K) the bandgap is  $E_g = 0.32eV$ , and it decreases with temperature to  $E_q = 0.18eV$  at 10K [23].

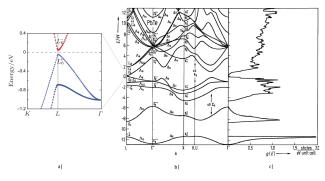

Fig. 5: Band structure of PbTe:

**a** Close-up of the band structure of PbTe around the direct bandgap at the L-point. Calculated using DFT by Wang et al. [39].

$\boldsymbol{b}|$  Full band structure and  $\boldsymbol{c}|$  density-of-states of PbTe, reprinted from [40].

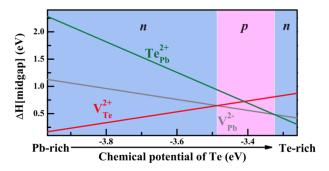

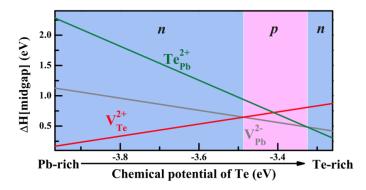

From experiments it has been reported that PbTe can be doped to be either p-type or n-type [41][42]. Native point defects are important doping mechanisms as these have quite low formation energies in PbTe [43]. Depending on how far the crystal deviates from stoichiometry, there are three possible defect states with the lowest formation energy (see fig.6:

- $V_{Te}^{2+}$ : In a Pb-rich crystal, Te vacancy has the lowest formation energy.

- $V_{Pb}^{2-}$ : If the crystal is slightly Te-rich, the Pb vacancy has the lowest formation energy.

- $Te_{Pb}^{2+}$  From DFT calculations Wang et al.[43] that the  $Te_{Pb}^{2+}$  antisite defect has the lowest formation energy for highly Te-rich crystals. In this defect type a tellurium atom replaces a lead atom in the crystal lattice.

If the dominant dopant is positively (negatively) charged, the intrinsic Fermi level is shifted towards the conduction (or valence) band, respectively. Therefore a PbTe crystal can be tuned from n-type to p-type and again to n-type by tuning the stoichiometry from Pb-rich to Te-rich [38][43][43][44][45].

Fig. 6: Midgap formation energy for the three lowest-energy defect states as a function of the chemical potential of Te. The lowest energy defect state determines the doping character of the crystal (blue: n-type, pink: p-type). As calculated by Wang et al.[43].

A last material property PbTe that is relevant to mention, is its high (low-frequency) dielectric constant  $(\epsilon(0) = 400)[23][46]$ . This results in strong Debye shielding of charged impurities in the PbTe nanowire, or at its interfaces with other material.

## II. NANOWIRE GROWTH

A myriad of chemical methods have been used to synthesise PbTe nanowires, such as electrodeposition , chemical vapour deposition and the chemical vapour transport method [47][48][49][50][51][33]. Especially this last method has yielded wires with good crystallinity and transport properties [52].

Molecular beam epitaxy (MBE) has been reported to yield defect-free PbTe thin-films [53][54]. This can be achieved by using ultrapure sources for the deposition of thin films under ultra-high vacuum (UHV) conditions. Consequently, films grown using MBE have been shown to yield significantly higher carrier mobilities than the chemical methods for wire growth [48][51][54]. Moreover, these reports show control over the intrinsic doping by changing the IV/VI (Pb/Te) flux ratio during the growth process. This determines the deviation from stoichiometry of the grown thin-film and therefore its doping character. It would be desirable to harness the properties of MBE growth for nanowires as well. Some work has been published on MBE growth of PbTe nanowires [55][56], which shows defect-free, but quite short (several 100 nm) and tapered nanowires.

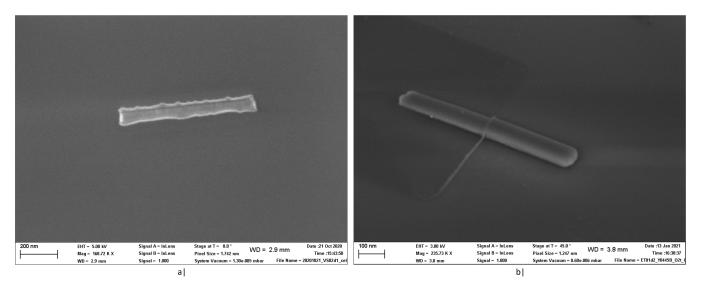

The nanowires used in this project were grown at the NanoLab@TU/e clean room at Eindhoven University of technology. These wires are single-crystalline, and significantly longer than the ones reported in other works (on average 2-3  $\mu$ m [26]). In the rest of this section, we will take a closer look at the growth mechanism and quality of these wires.

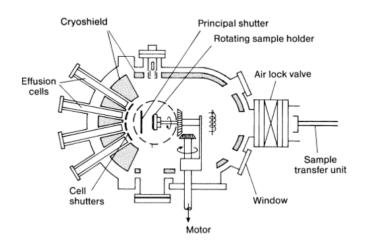

Fig. 7: Schematic depiction of a MBE system. Indicated are its most important component parts. Adapted from Ibach and Lüth [57]

The concept of a MBE system is quite simple. For a schematic depiction of an MBE system, see fig.7. A substrate is placed on a sample holder in an ultrahigh vacuum (UHV). Multiple effusion cells are positioned opposing the sample. The (precursor) material in these effusion cells is evaporated, and will propagate in to the chamber once the shutters are opened. Due to the quality

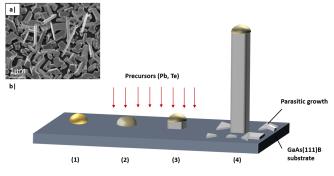

Fig. 8: VLS growth of PbTe nanowires.

precursor materials.

$\mathbf{a}$  [Inset: SEM image of PbTe nanowires grown using this growth mechanism. It can clearly be seen that the growth yields both nanowires and quite some parasitic growth on the substrate.

**b**| Schematic representation of the VLS mechanism of nanowire growth: (1) Catalytic gold droplets are patterned on the GaAs(111)B substrate. (2) Once the shutters are opened the substrate is bombarded with precursor material.

(3) This precursor material favours the formation of an alloy with the gold droplet over lateral film growth. Supersaturation of the gold droplet with the precursor results in nucleation an growth of the nanowire.(4) The growth catalysed by the alloy droplet results in wires that are much taller than the surrounding parasitic lateral growth.

of the UHV and the pressure gradient between the effusion cell and the UHV chamber, the substrate is bombarded by a ballistic beam of the precursor material(s) [57]. A film is deposited on the substrate, if the incoming flux is larger than the re-evaporation rate. Herein substrate temperature is an important parameter. The composition of the grown film can be controlled by the ratio of the incoming fluxes of the

The vapour-liquid-solid (VLS) mechanism [58] was used to grow gold-catalysed nanowires on GaAs(111)B substrates (see fig.8b). The gold droplets are pre-patterned onto the substrate using EBL en e-beam evaporation. During the growth process in the MBE system the precursor material (atomic Pb and Te) favours the formation of an alloy with the gold droplet over the nucleation of lateral film growth. Supersaturaton of the alloy droplet with the precursor material will lead to crystalline PbTe deposition under the droplet, lifting it up in the process. This process does not prevent lateral film nucleation and growth, but it does catalyse the wire growth.

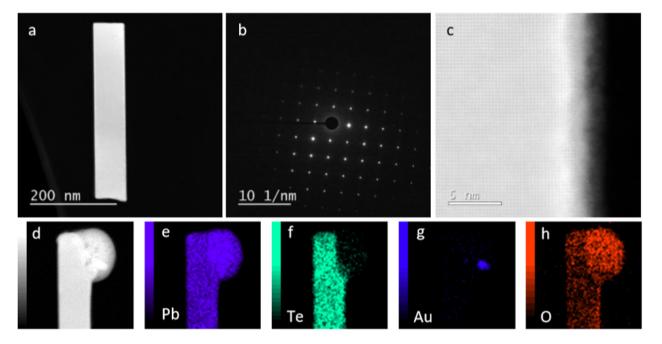

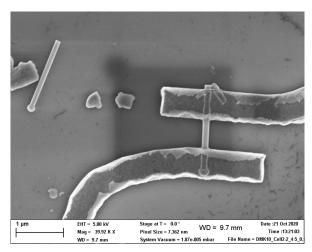

Dependent on the growth conditions the wires grow up to 3  $\mu$ m long, and have diameters of 80-120 nm [26]. In figure 9a a bright-field TEM image shows part of one of the PbTe nanowires. From the electron diffraction pattern (fig.9b) and close-up HAADF-STEM (fig.9c), it can be seen that the wires are indeed single-crystalline and defect-free. Figure 9d shows a close-up image of the top of a wire with the gold droplet. The composition of the wire and the catalytic gold droplet can be seen in the EDX maps shown in figures 9e-h.

From both the EDX maps and the close-up HAADF-STEM it can be seen that a native oxide with a thickness of a few nanometers is formed on the wires upon contact with air.

Fig. 9: (a) Bright field TEM image of a part of a MBE grown PbTe nanowire. (b) Electron diffraction pattern of the same nanowire. (c) HAADF-STEM image of the side of the nanowire. (d)-(h) EDX mapping Reprinted with permission from A.G. Schellingerhout [26].

# Nanowire MOSFET devices

The electrical properties of the PbTe nanowires are determined in field-effect measurements. To be able to perform these measurements, nanowire metal-oxide-semiconductor field-effect transistors (MOSFETs) are fabricated. In this chapter the working principles of these MOSFET devices will be explained. Working towards that goal, first the electric properties of semiconducting materials themselves will be discussed (section I). Then the interfaces between semiconductors and other materials will be described (section II). This is important to understand the influence of the contacts on the carrier transport through the device. Finally, the working principles of nanowire MOSFETs (section III will be explained. Some extra attention will be given to non-ideal behaviour, such as capacitance effects and subthreshold conduction.

## I. ELECTRONIC PROPERTIES OF SEMICONDUCTING MATERIALS

Before the entire device geometry is discussed, we will first take a look at the electronic properties of a (bulk) semiconductor material.

# A. Carrier densities

In an undoped (intrinsic) semiconductor the chemical potential  $\mu$  is lies at the centre of the band gap. This position is called the intrinsic Fermi level  $E_{F,i}$ . In such a material free charge carriers can only be created by means of thermal or optical excitation over the band gap. Such an excitation creates an electron-hole pair: an electron in the conduction band, and a hole in the valence band. In a similar process, an electron can relax back to the valence band and recombine with a hole. In this process energy is conserved through the emission of phonons and/or photons.

In thermal equilibrium, the excitation rate is equal to the recombination rate. This implies that the electron density  $\rho_n$  and hole density  $\rho_p$  are also equal. Therefore the intrinsic carrier density ( $\rho_i = \rho_n = \rho_p$ ) can be expressed as:

$$\rho_i = \sqrt{N_c N_v} \exp\left(\frac{-E_g}{2k_b T}\right) \,, \tag{16}$$

with  $N_v$  and  $N_c$  the effective density of states in valence and conductance bands, respectively. Here  $E_g$  is the band gap energy, and T the temperature.

The carrier density can be modified by introducing dopants to the material. These dopants are electrically active impurities, that either introduce additional electrons or holes to the system [57]. Donor states introduce extra electrons to the system. This results in  $\rho_n > \rho_p$ , therefore this is called an n-type semiconductor. The addition of electrons increases the radius of the Bloch sphere. Therefore the Fermi level shifts towards the conduction band.

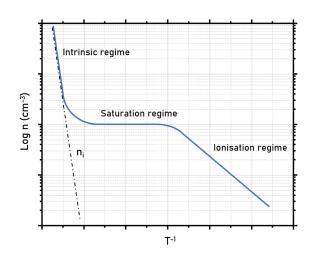

Acceptor states capture an electron from the valence band. This is equivalent to the introduction of extra holes. In such a p-type material the Bloch sphere shrinks due to the dopants, and the Fermi level will shift closer to the valence band. Fig.10 shows the (inverse) temperature dependence of the electron density in a n-type semiconductor. A similar curve can be sketched for holes in a p-type material. The temperature dependence can be divided into 4 different regimes:

- At very low temperatures, the extra electron/holes are bound to the donor/acceptor states. This is called the freeze-out regime: doping does not contribute to the carrier density, and also the intrinsic carrier density is negligible. The material behaves as an insulator.

- If the thermal energy is larger than the activation energy  $E_A$  needed to ionise the donors/acceptors, the carrier density will increase with temperature. This is called the ionisation regime: the majority carrier density can be described using an Arrhenius equation [59]:

$$\rho_{n/p} \propto \exp\left(\frac{-E_A}{k_b T}\right)$$

(17)

- The saturation regime is a temperature range where all donors/acceptors are ionised, but the contribution of the intrinsic carriers is still exceedingly small. The carrier concentration is approximately constant.

- Finally, at relatively high temperatures thermal excitation of intrinsic carriers starts to contribute significantly to the total carrier density.

Fig. 10: Electron density as a function of inverse temperature. Indicated are the intrinsic, saturation, and ionisation regimes. The dotted line indicates the temperature dependence of the carrier density for an intrinsic semiconductor.

## B. Electronic transport

Electronic transport is defined as the net flow of carriers under the influence of an electric field (drift) or a gradient in the carrier concentration (diffusion) [60]. In the nanowire MOSFET devices we consider here the field-driven current dominates [61]. The electronic current density is given by:

$$J_n = -e\rho_n v_d \,, \tag{18}$$

with  $v_d$  the drift velocity. This drift velocity is the average electron velocity, and is limited by scattering.

If only drift due to an electric field E is considered, the generalised force on an electron is given by:

$$m_e^* \frac{dv}{dt} = -eE\,,\tag{19}$$

with  $m^*$  and v the effective mass and velocity of an electron, respectively. In a steady-state approximation, this reduces to an equation for the drift velocity:

$$v_d = -eE\tau/m_e^*\,,\tag{20}$$

here  $\tau$  is the average time between scattering events. This scattering term limits the drift velocity. Here the electrons were considered as the majority carriers; a similar equation can be written down if holes are the majority carriers.

By combining equations 18 and 20, the current density can be expressed as a function of the applied electric field:

$$J = \sigma E \,, \tag{21}$$

where the conductivity  $\sigma$  is defined as:

$$\sigma = -e\rho_n\mu_n + e\rho_p\mu_p.$$

<sup>(22)</sup>

Here the actual response to the electric field is given by the carrier mobilities  $\mu_{n/p}$ :

$$\mu_{n/p} = e\tau/m_{n/p}^*, \qquad (23)$$

The carrier mobility is again limited by scattering. The dominant scattering processes are impurity and electronphonon scattering [59][62][63][64]. The electron-phonon scattering cross-section decreases with temperature, leading to a significant increase in carrier mobility [?].

#### **II. METAL-SEMICONDUCTOR INTERFACES**

The interfaces between different materials have an important effect on the transport of charge carriers through electronic devices. In this section the physics of material interfaces and the consequences for electronic transport will be discussed.

#### A. The Schottky-Mott model

The simplest model to describe the potential landscape for free charge carriers at an interface between two materials is the Schottky-Mott model. This model describes the alignment of the valence band maxima (VBM) and conduction band minima (CBM) between the two materials, based on a simple assumption: the system is in thermal and electrostatic equilibrium. In other words: no spontaneous currents flow through the system.

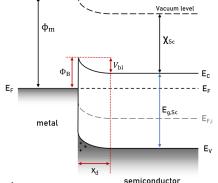

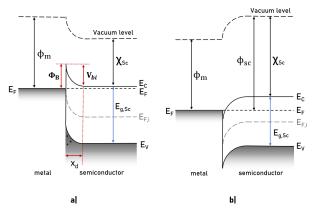

The energy bands of an isolated metal and an n-type semiconductor are shown in fig.11a. Both are aligned to the vacuum level. If the two materials are brought into contact, the Fermi level difference will induce the exchange of charge between the materials. This results in the build-up of a space-charge region at the interface. The potential drop over this interface compensates for the Fermi level difference, resulting in a system that is in electrostatic equilibrium. This band bending is shown in fig.11b.

The band bending results in an asymmetric potential barrier for electrons at the interface. The barrier the electrons encounter when moving from the metal into the semiconductor is called the Schottky barrier  $\Phi_B$ . This barrier height is defined solely by the work function of the metal  $\phi_m$  and the electron affinity of the semiconductor  $\chi_{sc}$ :

$$\Phi_B = \phi_m - \chi_{sc} \tag{24}$$

The built-in potential  $V_{bi}$  is the (unbiased) potential for electrons moving out of the semiconductor:

$$eV_{bi} = e\Phi_B - (E_F - E_c(bulk)).$$

<sup>(25)</sup>

This potential is a function of the distance between the Fermi level and the conduction band, and therefore depends on the doping density. The potential barrier  $(\Delta V)$  an electron

acuum level φ<sub>m</sub>  $\chi_{Sc}$ φm χ<sub>so</sub> Ec E. E En metal E<sub>g,Sc</sub> metal Εv E' semiconductor semiconductor a bl

Fig. 11: Energy band alignment at a metal-semiconductor interface for a n-type semiconductor. a Energy bands of the isolated metal and semiconductor aligned to the vacuum level. Specified are the metal work function

$\phi'_m$  and the semiconductor electron affinity  $\chi_{sc}$  and band gap  $E_{g,sc}$ . **b**| Band bending at a metal-semiconductor interface. Here also the Schottky barrier height  $\Phi_B$  and built-in potential  $V_{bi}$  are indicated in red.

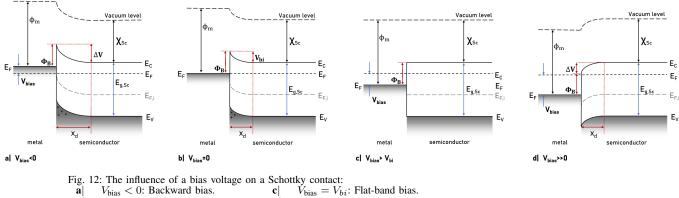

**b**  $V_{\text{bias}} = 0$ : No bias. **d**  $V_{\text{bias}} >> 0$ : Large forward bias

encounters when moving out of the semiconductor can be influenced by applying a bias voltage over the junction. Per definition, at zero bias this potential is equal to the built-in potential. A positive (forward) bias decreases the barrier height, and a negative bias enlarges the barrier height. This is shown for the hypothetical barrier discussed before in fig.12. For certain bias voltages ( $V_{\text{bias}} > V_{\text{bi}}$ ) an electron current can flow unimpeded from the semiconductor into the metal, but encounters a barrier the other way around: the metal-semiconductor interface forms a rectifying contact.

The specific band alignment shown in fig.12 results in the formation in Schottky contacts. However, for other material combinations another type of contact can be formed: the Ohmic contact. An Ohmic contact is defined to have a resistance that is negligibly small for a current in both directions, compared to the resistances of the materials themselves [65]. In practice a contact shows Ohmic behaviour, if the barrier height can be overcome by the thermal energy of the charge carriers (0.9 mV at 10K, 25.9 mV at 300K).

Ohmic contacts can be realised in two ways:

- If the semiconductor is heavily n-doped (p-doped), the Fermi level is positioned very close to the CBM (VBM). The resulting band bending is shown in fig.13a. This alignment creates a tunnel barrier at the interface that is approximately equal for charge carriers moving in both directions:  $\Phi_B \approx V_{bi}$ . The large doping density also effectively screens the bulk of the semiconductor from the metal. Therefore the depletion region will be fairly narrow, resulting in an effective tunnel barrier.

- All sketches shown in fig.11b, fig.12, and fig.13a show the formation of Schotkky barriers. All have in common that the work function of the metal is larger than the work function of the semiconductor. When the effect of surface states is ignored, this will always result in the formation of Schottky barriers in the conduction band. The opposite case will result in the formation of an Ohmic contact, as is sketched in fig.13b. In general, Schottky barriers form for n-type and p-type under conditions summarised in the table below:

|                      | n-type   | p-type   |

|----------------------|----------|----------|

| $\phi_m > \phi_{sc}$ | Schottky | Ohmic    |

| $\phi_m < \phi_{sc}$ | Ohmic    | Schottky |

The Schottky-Mott model is actually a quite naive description of an interface, as it only describes how bulk properties are modified near the interface. But it completely ignores any effect the surface itself may have. Therefore the contribution of intrinsic surface states, trapped charges, and other interface effects will be discussed in sec.II-C.

#### B. Mechanisms of electronic transport

Let us now consider a typical n-type Schottky barrier as depicted in fig.12. Two mechanisms contribute to the transport of electrons across such a barrier: field emission (tunneling) and thermionic emission.

*Field emission:* Field emission is the thermally-assisted tunneling of charge carriers through the (rounded) triangular barrier created by the band alignment [65][66]. This tunneling process is also known as Fowler-Nordheim tunneling. The tunneling current is given:

$$J_{FN} = e\rho_n v_R \Theta \,, \tag{26}$$

with  $\Theta$  the tunneling probability, and  $v_R$  the Richardson velocity:

$$v_R = \sqrt{\frac{k_B T}{2\pi m^*}} \,. \tag{27}$$

This is the average velocity of the electrons that approach the barrier.

Fig. 13: The two types of band alignment that yield Ohmic contacts (for a n-type semiconductor):

**a** A thin tunnel barrier created by a very high doping concentration. **b** Band alignment at zero bias for  $\phi_m < \phi_{sc}$ . The tunneling probability  $\Theta$  can be easily be derived from the time-independent Schrödinger equation in the WKB approximation for a slowly varying potential [67][68]:

$$\psi(x) = \psi(0) \exp\left[-\int_0^x \frac{\sqrt{2m^*[V(x') - E]}}{\hbar} dx'\right], \quad (28)$$

For a triangular barrier with a width  $\delta$ :

$$V(x) - E = e\Phi_B^0(1 - x/\delta),$$

(29)

the tunneling probability can be expressed as:

$$\Theta = \frac{\psi(\delta)\psi^*(\delta)}{\psi(0)\psi^*(0)}$$

=  $\exp\left[-2\int_0^\delta \frac{\sqrt{2m^*}}{\hbar}\sqrt{e\Phi_B^0\left(1-\frac{x}{\delta}\right)}dx\right]$  (30)

=  $\exp\left[-\frac{4}{3}\frac{\sqrt{2m^*e\Phi_B^0\delta}}{\hbar}\right]$

The tunneling probability, and thus the tunnel current increasing for larger negative bias voltages, as this changes the aspect ratio of the triangular barrier. The tunneling current also increases with the doping concentration as this decreases the depletion region/tunnel barrier width. At doping concentrations than  $10^{18}$  cm<sup>-3</sup> field emission dominates the carrier transport (at small bias voltages). The tunneling current also increases with temperature. However, at high temperatures thermionic emission becomes the dominant transport process.

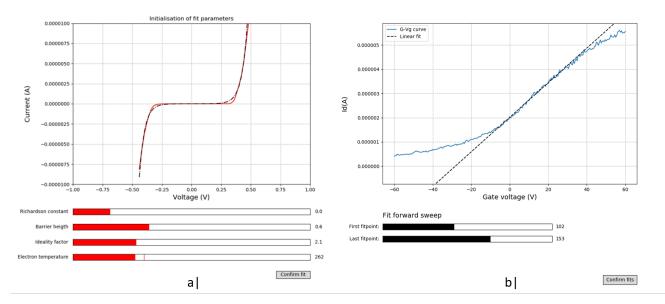

*Thermionic emission:* Thermionic emission is the emission of hot electrons into the vacuum, or in the case of a metal-semiconductor interface: into the empty conduction band of the semiconductor [59][65][69]. For low bias voltages the thermionic emission current is given by:

$$I_{TE} = A^{**}T^2 \exp\left(-\frac{e\Phi_B^0}{k_B T}\right) \left[\exp\left(\frac{eV_{bias}}{k_B T}\right) - 1\right] \quad (31)$$

with  $A^{**}$  the product of the interface area and the effective Richardson constant  $A_R^*$  [70]. This model has been shown to be in good agreement for many material systems at non-cryogenic temperatures [71][72][73][74].

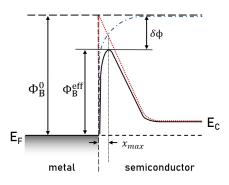

However, this model can be refined to include some interface effects. One important barrier lowering mechanism is the Schottky effect. Free charges in the semiconductor induce a surface charge at the metal interface to shield the bulk metal. The resulting electric field can be expressed in terms of mirror charges. In addition to the potential due to the mirror charge, the charge distribution in yhe depletion region contributes to the potential landscape for an electron in the conduction band of the semiconductor. For now the field due to the depletion region will be denoted by  $E_0$ . In sec.III-A the depletion region will be discussed in more detail. For an electron at a distance x from the interface, the potential due to the mirror charge and the depletion region can now be expressed as:

$$V(x) = \frac{e}{16\pi\epsilon_{sc}x} - E_0 x \tag{32}$$

Fig. 14: Barrier lowering due to the Schottky effect. Sketched are the potentials due to the image charge (blue dash-dotted line), and due to the depletion region (red dotted line), both relative to the unperturbed barrier height  $\Phi_B^0$ . The resulting barrier is sketched in black. Indicated are the barrier lowering  $\delta\phi$  and the effective barrier height  $\Phi_B^{\rm eff}$ .

This potential will have a maximum at position  $x_{max}$ , close to the interface:

$$x_{max} = \sqrt{\frac{e}{16\pi\epsilon_{sc}E_0}}.$$

(33)

Substituting this back into eq.32 yields a lowering of the barrier:

$$\delta\phi = \sqrt{\frac{eE_0}{4\pi\epsilon_{sc}}}\tag{34}$$

The resulting barrier is sketched in fig.14. The effective Schottky barrier height can now be expressed as:

$$\Phi_B^{\rm eff} = \Phi_B^0 - \delta\phi \,. \tag{35}$$

Note that the barrier lowering implicitly depends on the applied bias voltage through the band bending/depletion region width. This dependence can be quantified through the ideality factor n [60][70][75]:

$$n = \left(1 - \frac{\partial \Phi_B^{\text{eff}}}{\partial V_{bias}}\right)^{-1} \tag{36}$$

Using both the effective barrier height and the ideality factor, the thermionic emission current can be expressed as:

$$I_{TE} = A^{**}T^{2} \exp\left(-\frac{e\Phi_{B}^{\text{eff}}}{k_{B}T}\right) \exp\left(\frac{eV_{bias}}{nk_{B}T}\right) \times \left[1 - \exp\left(-\frac{eV_{bias}}{k_{B}T}\right)\right]$$

(37)

For  $\Phi_B^{\text{eff}} = \Phi_B^0$  and n = 1, this reduces to eq.31.

A last remark: the Schottky barrier height is not necessarily constant over the interface. Surface roughness can result in local field enhancement, and therefore in stronger Schottky barrier lowering. The ideality factor n is the average barrier lowering due to a bias voltage, and therefore depends also implicitly on the surface roughness: the cleaner the interface, the lower the ideality factor will be [70].

# C. Surface states and Fermi level pinning

Up until this point we have treated the contact formation between the metal and the semiconductor as a semiclassical electrostatic problem. This is useful for the description of macroscopic and mesoscopic phenomena, such as carrier transport. However, a microscopic description of the actual interface can illuminate the shortcomings of the Schottky-Mott model and describe the interface formation a lot more accurately. Several types of electronic states can form at the interface. The density of these surface states and their occupation determine the band alignment, and therefore the behaviour of the contact formation.

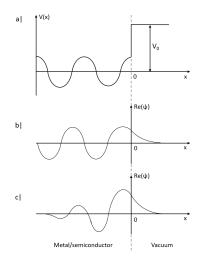

Intrinsic surface states arise from the broken translational symmetry at the surface. The wave function of an electron in a semi-infinite perfect crystal is invariant under translation with the period of of the crystal in both directions parallel to the interface. Therefore the investigation of the surface reduces to a one-dimensional problem. The potential in the direction perpendicular to the interface is given by:

$$V(x) = \begin{cases} V_c \cos\left(\frac{2\pi x}{a}\right) & x < 0\\ V_0 & x > 0 \end{cases},$$

(38)

which is periodic (with period a in the crystal and constant outside it, as is shown in fig.15a.

Now the Schrödinger equation can be solved for this potential. An electron in the crystal will back scatter elastically when it hits the surface. Therefore the general the wave function inside the crystal  $\psi_c$  can be expressed as a superposition of two counterpropagating waves with wave vectors  $\kappa \pm \pi/a$ :

$$\psi_c = A e^{i(\kappa + \pi/a)x} + B e^{i(\kappa - \pi/a)x} \tag{39}$$

Outside the crystal the wave function decays exponentially:

$$\psi_0 = C \exp\left(-\sqrt{\frac{2m}{\hbar^2}(V_0 - E)}x\right) \tag{40}$$

Fig. 15: A model for the interface of a crystalline conducting solid  $\mathbf{a}$  | Sketch of the semi-infinite Bloch potential that models the edge of the crystal.

$\mathbf{b}$ | The resulting Bloch wave that decays exponentially into the vacuum.  $\mathbf{c}$ | Solution to the Schrödinger equation for an imaginary k-vector: this allows for the formation of a surface resonance. The general solution to the Schrödinger equation in all space requires that the values of the wave functions and their first derivatives to the relevant spatial coordinate match. This solution is sketched in fig.15b: it is just a Bloch wave that decays into the vacuum. The electronic energy levels of these states are slightly modified with respect to their bulk values

Additional solutions are possible if we allow for imaginary  $\kappa$ . The resulting wave functions decay in *both* directions, as is shown in fig.15c. These surface resonances are therefore confined within a few Ångstrom from the interface. One can also look at the termination of a crystal in the Linear Combination of Atomic Orbitals (LCAO) framework. Then these surface states correspond to the concept of dangling bonds. The problem described above, is treated in much more detail by e.g. Lüth [76].

Similar interface states are formed in the semiconductor band gap at a metal-semiconductor interface. The tails of the wavefunctions of the delocalised electrons in the metal decay into the semiconductor band gap: electronic states are formed in the band gap at the interface. These surface states are named Metal-Induced Gap States (MIGS), and they are an intrinsic consequence of the breaking of the translational symmetry perpendicular to the surface.

Next to these intrinsic surface states, also extrinsic surface states exist. These extrinsic states are electronic states that are charged/trap charges, which are caused by imperfections or defects on the interface [76][77].

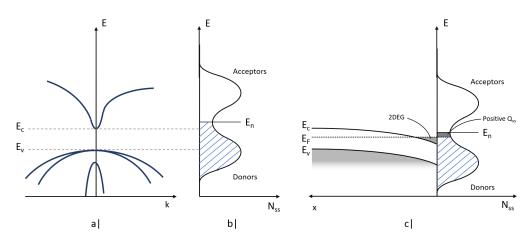

Fig.16a and b show sketch of a part of the band gap of a narrow band gap semiconductor, and the resulting density of surface states  $N_{ss}$ . Indicated is the branch point energy  $E_n$ . The surface states below this energy behave as donors: they are neutral when they are occupied, and positively charged if this is not the case. The states above the branch point are acceptor-like.

The position of the Fermi level relative to relative to this branch point determines the sign and amount of net charge on the interface. This surface charge is the microscopic origin the band bending described by the Schottky-Mott rule, and thus determines the Schottky barrier height [57]. The barrier height and the surface density of states  $N_{ss}$  can be related through:

$$E_g - e\Psi_s - e\Phi_B = \frac{1}{eN_{ss}\sqrt{2e\epsilon_{sc}N_{d/a}(\Phi_B - \phi_n)}} - \frac{\epsilon_i}{eN_{ss}\delta}(\phi_m - \chi_{sc} - \Phi_B)$$

(41)

with the surface potential  $\Psi_s$  the difference between the intrinsic Fermi level at the interface and in the bulk (see sec.III-A). The interface is modelled in this expression as a very thin dielectric layer which is transparent for electron transport. This interface layer has a thickness  $\delta$  (O(Å)), and an effective dielectric constant  $\epsilon_i$ .

Fig. 16: Fermi level pinning in narrow band gap semiconductors

$\boldsymbol{a}|$  Sketch of the band gap of an arbitrary narrow band gap semiconductor.

$\mathbf{b}$  Surface state density resulting from the dispersion in  $\mathbf{a}$ .

c Band bending caused by the positioning of the Fermi level in the surface DOS. A 2DEG is formed at the interface by pinning the Fermi level in the conduction band. The charges of the surface states and the 2DEG are equal in magnitude.

Two limiting cases for this model can be examined:

1)  $N_{ss}\delta \rightarrow 0$ : the interface layer disappears. In this case the expression above reduces to the familiar Schottky-Mott rule:

$$\Phi_B = \phi_m - \chi_{sc} \tag{42}$$

N<sub>ss</sub> → ∞: The surface charge density dominates the band bending. In this case the Fermi level gets pinned at in the band gap at the surface potential Ψ<sub>s</sub>:

$$\Phi_B = \frac{1}{e} (E_g - e\Psi_s) \tag{43}$$

This Fermi level pinning is very important in the determination of the Schottky barrier height [76][78][79]. However, the surface density of states  $N_{ss}$  cannot easily be determined, either experimentally or analytically.

Generally Fermi level pinning is a dominant effect in narrow band gap semiconductors, such as InAs and InSb [80]. Fig.16a and b show a sketch of a the band gap of such a semiconductor, and the resulting IFIGS density. Because of the position of the Fermi level in this surface DOS, the donor states between the Fermi level and the branching point are unoccupied; a positive surface charge exists, independent of any metal that ma be used for contact formation. The conduction band is then dragged below the Fermi level: a two-dimensional electron gas (2DEG) is formed at the interface to shield the semiconductor from the surface charge.

This has for example been verified for InAs: the Fermi level pinned into the conduction band by about 50meV [81][82].

Several groups have investigated Fermi level pinning and its influence on contact formation on PbTe, and report conflicting results. Lai and Cerrina et al. performed cyclotron photo-electron spectroscopy experiments to investigte metal-PbTe interfaces [83][84]. After cleaving PbTe crystals in UHV, several metals were deposited in-situ on the cleave (100) surface. They found generally no correlation between  $\Phi_B^0$  from expected from the Schottky-Mott rule and the experimental values. This indicates that surface charges play an important role. Interesting to note is that generally no atomically abrupt surfaces are formed during the metal deposition: several metals interdiffusion or even the formation of complexes with Te extracted from the substrate. This creates an extended interface layer whose barrier formation is difficult to predict. The exception was gold as a contacting metal: this formed an abrupt, nonreacted interface on the PbTe sample.

In contrast to these results: Walpole and Nill found some unpredictable band bending, but no Fermi level pinning on PbTe in their C-V and I-V electrical characterisation of several metal-PbTe interfaces [85].

#### III. WORKING PRINCIPLES OF THE NANOWIRE MOSFET

In the most general terms, a transistor is a device where one terminal (the gate) controls the current that flows between two other terminals (the source and drain). One of the most common types of transistor is the Metal-Oxide-Semiconductor Field-Effect Transistor, or MOSFET.

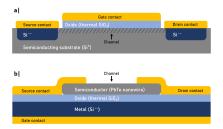

Conventional MOSFET devices, as sketched in fig.17a, are fabricated on a doped semiconducting substrate. Using techniques like ion bombardment the doping density in the substrate can locally be changed to form metallic regions. These areas can be used as the source and drain contacts of the MOSFET. The area between the contacts then forms the channel. An insulating oxide layer with a third contact, the gate, are deposited on top of this channel. By applying a potential to the gate, the charge density can be modulated in the channel between the source and drain contacts.

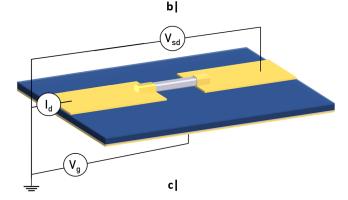

The design of nanowire MOSFET flips the MOS stack upside down (see fig.17b). A degenerately doped (metallic) silicon substrate with a back contact is used as a gate. The thermal oxide functions as the insulating layer. Then a semiconducting nanowire is transferred on top, completing the MOS stack. Metallic leads are deposited directly on top of the semiconducting nanowire to form the source and drain contacts. Despite the inverted design, the working principles of both designs are identical.

Fig. 17: Schematic cross-section of two MOSFET designs: **a**| Conventional MOSFET: the source and drain contacts are formed by ion implantation in the semiconducting substrate. The substrate, an insulating oxide layer, and a metal gate contact form the MOS stack. The carrier density in the channel (shaded area in the substrate) can be influenced by applying a potential on the gate. The particular device sketched here is a n-channel enhancement mode MOSFET [59]. **b**| Nanowire MOSFET: The oxidised Si<sup>--</sup> substrate with the PbTe nanowire on top together form the MOS stack. The addition of source and drain contacts on the nanowire, and a gate contact on the heavily doped substrate, completes the device architecture.

#### A. MOS stack: gate behaviour

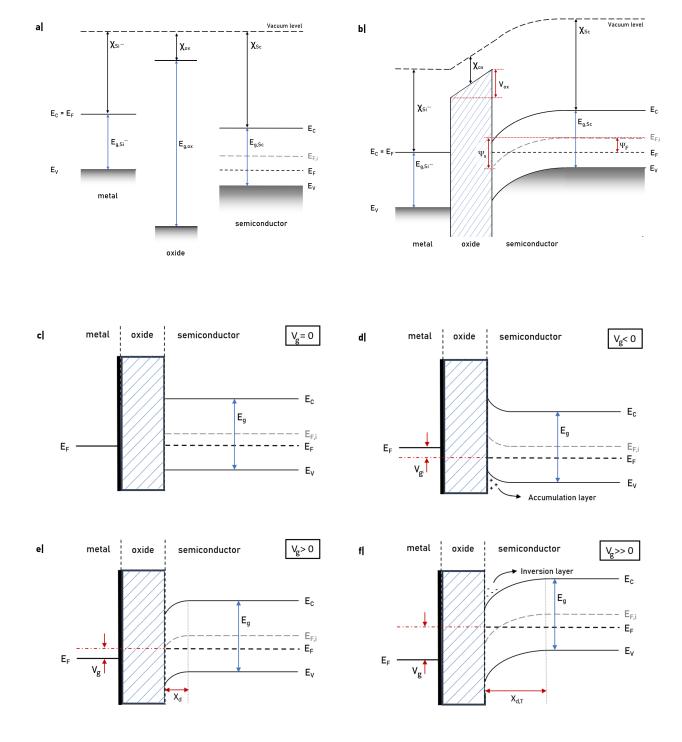

For now let us ignore the source and drain contacts, and examine just the metal-oxide-semiconductor stack. Fig.18a shows the energy bands of the different layers of the MOS stack in isolation. Here, a heavily n-doped (metallic) semiconductor acts as the metal, as  $Si^{--}$  substrates are used in this project.

According to the Schottky-Mott model (see sec.II) the energy bands will deform close to an interface between different materials [59]. The Fermi levels in the metal and semiconductor will line up to satisfy electrostatic equilibrium; no spontaneous current will flow. In contrast to the metal-semiconductor interface discussed before, no charge exchange between the metal and semiconductor can take place due to the presence of the insulating oxide layer. This results in the formation of space-charge regions at the metal-oxide and oxide-semiconductor interfaces. The charge accumulation results in the bending of the bands:

- The charge density in the metallic layer is quite large, and will therefore be effectively screened from external charges or potentials. No space-charge region will be formed in the metal: charges will accumulate only at the metal-oxide interface.

- The absence of free carriers in the oxide will result in an electrostatic potential  $V_{ox}$  over the oxide layer.

- The smaller charge density in the semiconductor will result in the formation of a space-charge region at the oxide-semiconductor interface. This will be discussed in more detail below.

The band alignment for the layers in fig.18a is sketched in fig.18b.

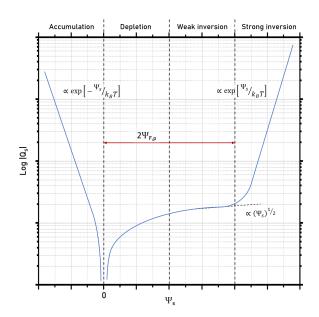

For a further discussion of the band bending in the MOS stack, two important potentials need to be defined: the Fermi potential  $\Psi_F$  and the surface potential  $\Psi_s$ . Both are indicated in the band diagram in fig.18b.

The Fermi potential is defined as the difference between the intrinsic Fermi level  $E_{F,i}$  and the actual Fermi level  $E_F$  in the bulk of the semiconductor, and can thus be regarded as

a measure for the doping of the semiconductor:

$$e\Psi_F = E_{F,i} - E_F \tag{44}$$

$$=k_B T \exp\left[\frac{N_{d/a}}{n_i}\right] \tag{45}$$

Here  $N_{d/a}$  is the donor/acceptor density, respectively.

The surface potential quantifies the band bending in the system. It is defined as the difference between the intrinsic Fermi level in the bulk and at the interface:

$$e\Psi_s = E_{F,i}(\text{surface}) - E_{F,i}(\text{bulk})$$

(46)

Especially this surface potential plays a central role in the description of (the modification of) the band alignment.

The band bending, and therefore the accumulation of charge at the oxide-semiconductor interface, can be influenced by applying a potential over the MOS stack. The effect of this gate voltage  $V_g$  can be described by:

$$V_g = V_{ox} + \Psi_s + \phi_{ms} \tag{47}$$

The work function difference between the metal  $(Si^{--})$ and semiconductor  $\phi_{ms}$  is completely defined by the semiconductor band gap  $(E_{g,sc})$  and doping, and the electron affinities of both materials  $(\chi_{Si^{--}}, \chi_{sc})$ :

$$\phi_{ms} = \chi_{Si^{--}} - \left[\chi_{sc} + \frac{E_{g,sc}}{2e} + \Psi_F\right] \tag{48}$$

This expression is independent of the applied voltage. Therefore the oxide and surface potentials, and thus the band bending, are directly influenced by the gate.

An important value of the gate voltage is the flat-band voltage. This is the gate potential needed to counteract the band bending caused by the Fermi level alignment:

$$\Psi_s = V_{ox} = 0. \tag{49}$$

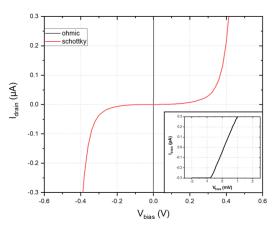

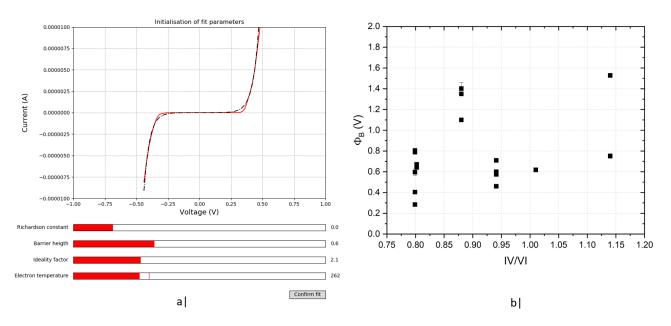

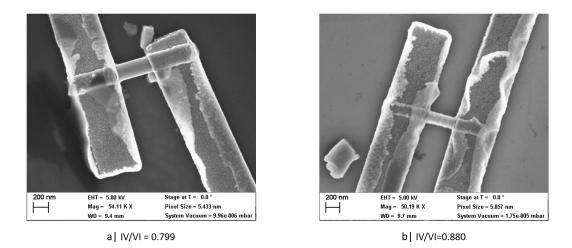

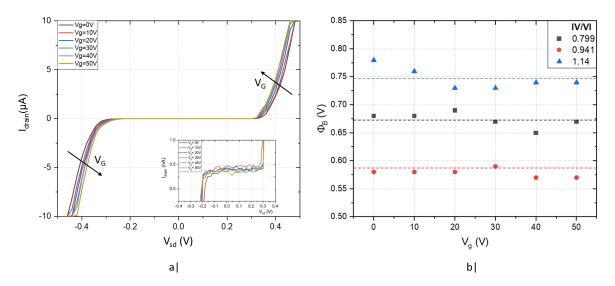

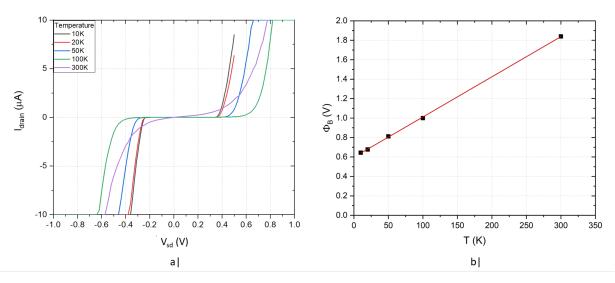

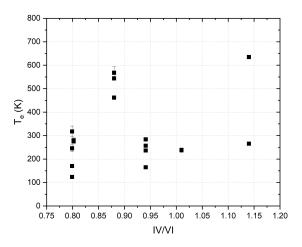

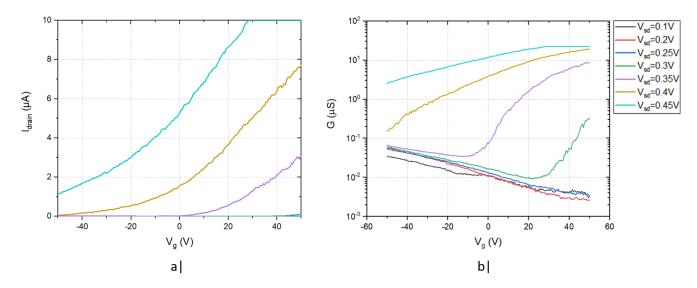

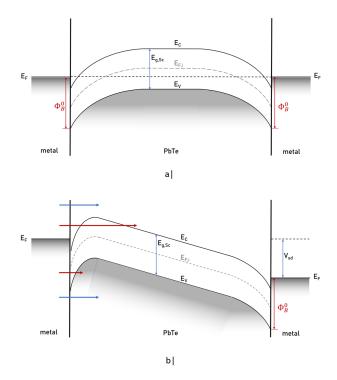

In this case no space-charge regions are present in the entire MOS stack.